台積電攻扇出型面板級封裝 估3年後成熟就緒

2024/7/18 16:23(7/18 16:38 更新)

(中央社記者鍾榮峰台北18日電)晶圓代工龍頭台積電積極布局先進封裝,董事長魏哲家今天表示,台積電持續研發扇出型面板級封裝(FOPLP)技術,預期3年後技術可成熟,屆時台積電可準備就緒。

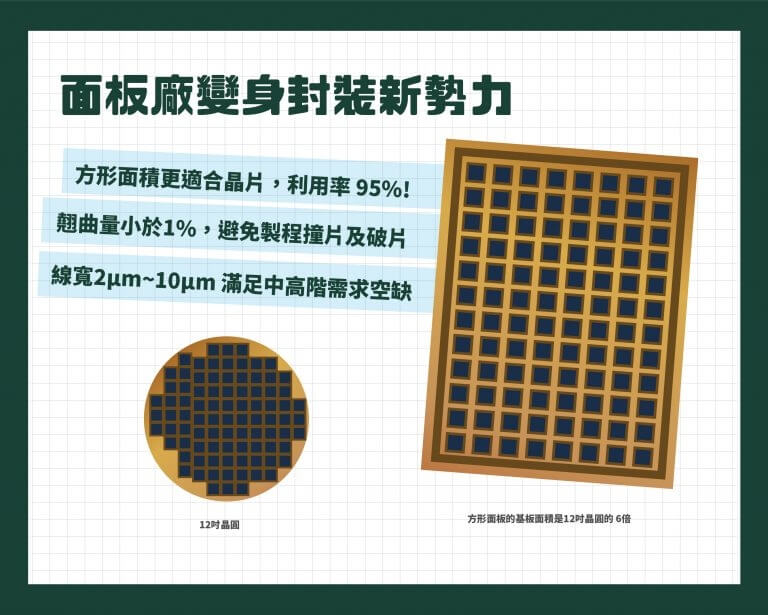

台積電下午舉行實體法人說明會,法人詢問台積電在CoWoS以外其他先進封裝技術布局。魏哲家表示,台積電持續關注扇出型面板級封裝(FOPLP)技術,不過相關技術目前還尚未成熟;他個人預期3年後FOPLP技術可望成熟,台積電持續研發FOPLP技術,屆時可準備就緒。

CoWoS小百科

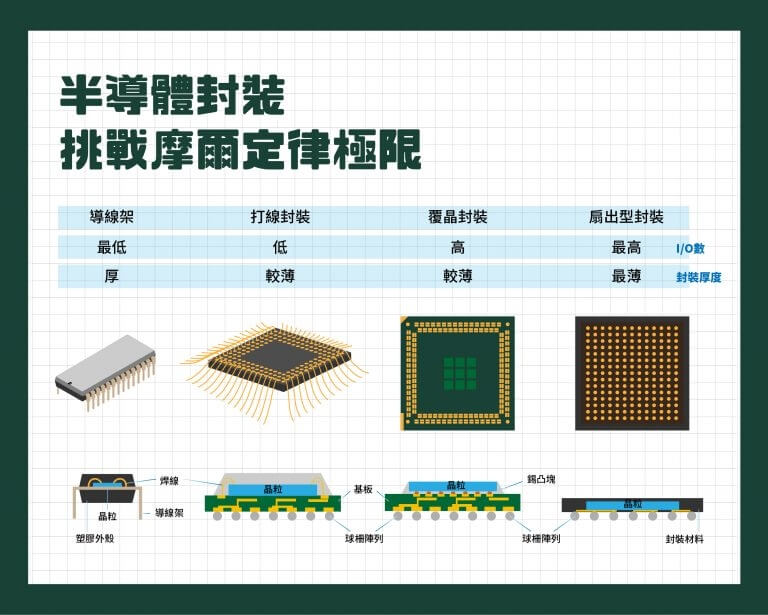

CoWoS是一種半導體的先進封裝技術,可以拆成CoW和WoS。CoW(Chip-on-Wafer)指的是「晶片堆疊」、WoS(Wafer-on-Substrate)則是將晶片堆疊在基板上,可提高晶片間的數據傳輸速度。

透過先進封裝技術的進步,晶片製造商有望持續提升晶片效能,繞過3奈米製程逐漸遇到物理極限瓶頸的問題。

看更多

關閉

市調機構集邦科技在7月上旬表示,台積電在2016年開發名為InFO的扇出型晶圓級封裝(FOWLP)技術,並應用在蘋果(Apple)iPhone 7的A10處理器,吸引封測業者跟進發展FOWLP及FOPLP技術。

集邦科技指出,晶圓代工廠及封測廠將人工智慧繪圖處理器(AI GPU)2.5D封裝模式,從晶圓級轉換至面板級,以超微(AMD)及輝達(NVIDIA)與台積電、矽品洽談AI GPU產品,最受矚目。

封測廠也正開發消費性IC封裝轉換為FOPLP,集邦科技表示,超微與力成和日月光洽談電腦中央處理器(CPU)產品,高通(Qualcomm)與日月光洽談電源管理晶片。

力成積極布局FOPLP和CMOS影像感測元件(CIS)等先進封裝,在面板級封裝持續與大客戶合作,在CIS的TSV晶圓級封裝技術(TSV CSP)封裝,與客戶合作量產。(編輯:張良知)1130718

本網站之文字、圖片及影音,非經授權,不得轉載、公開播送或公開傳輸及利用。